HBM 한계 넘는 낸드 기반 신개념 메모리 부상

하이닉스·샌디스크, 표준화 선도…삼성은 내부 개발 시사차세대 인공지능(AI) 메모리 시장의 새 주인공으로 고대역폭 낸드(HBF·High-Bandwidth Flash) 가 떠오르고 있다.

삼성전자와 SK하이닉스, 샌디스크(웨스턴디지털 자회사)가 나란히 HBF 개발에 뛰어들면서 ‘포스트 HBM’ 경쟁이 본격화했다는 평가다.

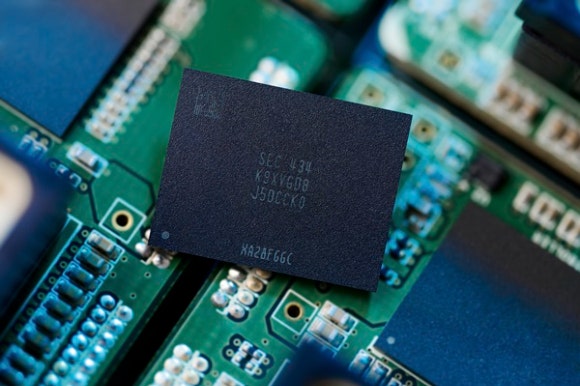

삼성전자 'QLC 9세대 V낸드' 제품 이미지. [사진=삼성전자]

28일 반도체 업계에 따르면 삼성전자·SK하이닉스·샌디스크는 D램을 수직 적층해 만든 고대역폭메모리(HBM)처럼 낸드를 적층한 HBF 기술 개발에 집중하고 있다.

HBM은 AI 서버용 그래픽처리장치(GPU)에 직접 붙는 D램 패키지로 초고속 대역폭을 자랑하지만, 비용과 용량 한계로 확산 대응에는 제약이 있었다.

이에 낸드의 대용량·저비용 특성을 살려 HBM 하단 계층을 보완하는 신개념 메모리 HBF가 주목받고 있다.

HBM이 초고속 연산을 담당한다면 HBF는 대규모 데이터 저장과 효율적 전송을 맡는 ‘보조축’ 역할이다.

속도는 HBM의 80~90% 수준이지만 용량은 8~16배, 전력소모는 약 40% 낮아 대규모 AI 학습·추론 서버에서 HBM 병목을 완화할 ‘중간층 메모리(Mid-Tier Memory)’ 로 평가된다.

김정호 카이스트 전기및전자공학부 교수는 “삼성전자, SK하이닉스, 샌디스크 3사가 차세대 AI 메모리로 HBF 기술을 개발 중”이라며 “향후 HBF가 HBM에 맞먹는 비중을 가질 것”이라고 말했다.

김천성 SK하이닉스 부사장이 지난 13~16일(현지시간) 미국 캘리포니아주 새너제이(San Jose)에서 진행된 '2025 OCP(오픈 컴퓨트 프로젝트) 글로벌 서밋’ 행사에 참가해 차세대 낸드 스토리지 제품 전략을 발표하는 모습.[사진=SK하이닉스]

가장 발 빠른 곳은 SK하이닉스다. SK하이닉스는 지난 8월 샌디스크와 HBF 기술 공동 개발 및 표준화 양해각서(MOU)를 체결했다.

시장조사업체 트렌드포스에 따르면 올해 2분기 글로벌 낸드 시장 매출 점유율은 △삼성전자 32.9% △SK하이닉스(솔리다임 포함) 21.1% △키옥시아 13.5% △마이크론 13.3% △샌디스크 12.2% 로 집계됐다. 낸드 2위와 5위가 차세대 AI 메모리 동맹을 맺은 셈이다.

양사는 사양 정의, 인터페이스 규격 통일, 생태계 구축을 공동 추진하며 2026년 하반기 샘플 칩 출시, 2027년 초 AI 장비 적용을 목표로 잡았다.

SK하이닉스는 최근 미국 ‘OCP 글로벌 서밋’에서 HBF 기술을 공개하고 이를 자사 ‘AIN 패밀리’ 전략의 핵심으로 규정했다.

샌디스크는 이 자리에서 “AI 서버 메모리 구조의 새 표준을 정의하겠다”며 HBF 전용 컨트롤러와 병렬 I/O 기술을 선보였다.

업계 관계자는 “SK하이닉스가 HBM에서는 세계 최고 수준이지만, 낸드는 삼성전자가 기술 및 점유율 모두 앞서 있다”며 “SK하이닉스가 샌디스크와 손잡은 건 부족한 낸드 역량을 보완하려는 전략적 결단으로 보인다”고 말했다.

송재혁 삼성전자 최고기술책임자(CTO)가 지난 22일 서울 강남구 코엑스에서 열린 반도체 대전 키노트 행사에서 기조 강연을 하는 모습. 송 CTO는 이날 기술의 융합 시너지에 대해 강연했지만, HBF를 내부적으로 준비 중이라는 단서를 남겼다.[사진=박지은 기자]

삼성전자도 내부적으로 HBF 연구개발에 속도를 내고 있는 것으로 전해진다.

공식 발표는 없지만, 최근 송재혁 삼성전자 최고기술책임자(CTO)의 발언이 단서를 남겼다.

송 CTO는 반도체대전 기조연설에서 “플래시까지도 상당한 스피드를 요구받고 있으며 곧 칩 간 멀티 본딩으로 진화해야 한다”고 말하며 HBF 연관 기술을 시사했다.

그는 “플래시·D램·로직의 경계가 사라지고 있다”며 패키징 단위의 융합을 강조했다.

이는 삼성이 낸드플래시를 기반으로 HBM 하위 계층을 보완하는 ‘고대역폭 낸드’ 개념을 내부적으로 추진하고 있음을 암시한다.

업계에서는 삼성이 자사 3D V-NAND 적층 기술과 TSV(Through-Silicon Via) 본딩 역량을 활용해 ‘HBM + HBF 하이브리드 패키지’ 구조를 준비하고 있다는 관측도 나온다.

하이닉스·샌디스크, 표준화 선도…삼성은 내부 개발 시사차세대 인공지능(AI) 메모리 시장의 새 주인공으로 고대역폭 낸드(HBF·High-Bandwidth Flash) 가 떠오르고 있다.

삼성전자와 SK하이닉스, 샌디스크(웨스턴디지털 자회사)가 나란히 HBF 개발에 뛰어들면서 ‘포스트 HBM’ 경쟁이 본격화했다는 평가다.

28일 반도체 업계에 따르면 삼성전자·SK하이닉스·샌디스크는 D램을 수직 적층해 만든 고대역폭메모리(HBM)처럼 낸드를 적층한 HBF 기술 개발에 집중하고 있다.

HBM은 AI 서버용 그래픽처리장치(GPU)에 직접 붙는 D램 패키지로 초고속 대역폭을 자랑하지만, 비용과 용량 한계로 확산 대응에는 제약이 있었다.

이에 낸드의 대용량·저비용 특성을 살려 HBM 하단 계층을 보완하는 신개념 메모리 HBF가 주목받고 있다.

HBM이 초고속 연산을 담당한다면 HBF는 대규모 데이터 저장과 효율적 전송을 맡는 ‘보조축’ 역할이다.

속도는 HBM의 80~90% 수준이지만 용량은 8~16배, 전력소모는 약 40% 낮아 대규모 AI 학습·추론 서버에서 HBM 병목을 완화할 ‘중간층 메모리(Mid-Tier Memory)’ 로 평가된다.

김정호 카이스트 전기및전자공학부 교수는 “삼성전자, SK하이닉스, 샌디스크 3사가 차세대 AI 메모리로 HBF 기술을 개발 중”이라며 “향후 HBF가 HBM에 맞먹는 비중을 가질 것”이라고 말했다.

가장 발 빠른 곳은 SK하이닉스다. SK하이닉스는 지난 8월 샌디스크와 HBF 기술 공동 개발 및 표준화 양해각서(MOU)를 체결했다.

시장조사업체 트렌드포스에 따르면 올해 2분기 글로벌 낸드 시장 매출 점유율은 △삼성전자 32.9% △SK하이닉스(솔리다임 포함) 21.1% △키옥시아 13.5% △마이크론 13.3% △샌디스크 12.2% 로 집계됐다. 낸드 2위와 5위가 차세대 AI 메모리 동맹을 맺은 셈이다.

양사는 사양 정의, 인터페이스 규격 통일, 생태계 구축을 공동 추진하며 2026년 하반기 샘플 칩 출시, 2027년 초 AI 장비 적용을 목표로 잡았다.

SK하이닉스는 최근 미국 ‘OCP 글로벌 서밋’에서 HBF 기술을 공개하고 이를 자사 ‘AIN 패밀리’ 전략의 핵심으로 규정했다.

샌디스크는 이 자리에서 “AI 서버 메모리 구조의 새 표준을 정의하겠다”며 HBF 전용 컨트롤러와 병렬 I/O 기술을 선보였다.

업계 관계자는 “SK하이닉스가 HBM에서는 세계 최고 수준이지만, 낸드는 삼성전자가 기술 및 점유율 모두 앞서 있다”며 “SK하이닉스가 샌디스크와 손잡은 건 부족한 낸드 역량을 보완하려는 전략적 결단으로 보인다”고 말했다.

삼성전자도 내부적으로 HBF 연구개발에 속도를 내고 있는 것으로 전해진다.

공식 발표는 없지만, 최근 송재혁 삼성전자 최고기술책임자(CTO)의 발언이 단서를 남겼다.

송 CTO는 반도체대전 기조연설에서 “플래시까지도 상당한 스피드를 요구받고 있으며 곧 칩 간 멀티 본딩으로 진화해야 한다”고 말하며 HBF 연관 기술을 시사했다.

그는 “플래시·D램·로직의 경계가 사라지고 있다”며 패키징 단위의 융합을 강조했다.

이는 삼성이 낸드플래시를 기반으로 HBM 하위 계층을 보완하는 ‘고대역폭 낸드’ 개념을 내부적으로 추진하고 있음을 암시한다.

업계에서는 삼성이 자사 3D V-NAND 적층 기술과 TSV(Through-Silicon Via) 본딩 역량을 활용해 ‘HBM + HBF 하이브리드 패키지’ 구조를 준비하고 있다는 관측도 나온다.

댓글목록

등록된 댓글이 없습니다.